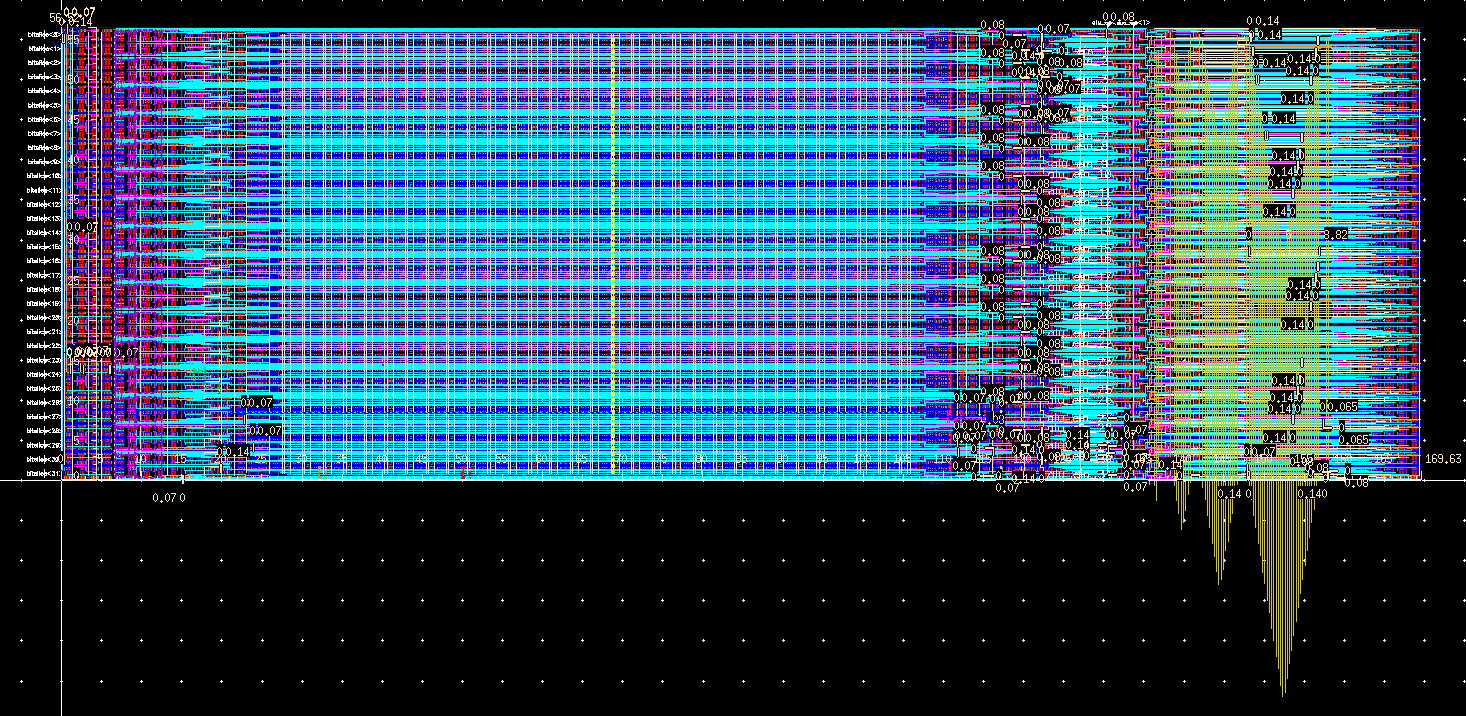

32-bit RISC-V Datapath Layout

a 32-bit datapath including alu, regfile, shifter, etc.

Overview

For ECE 425’s MP2, I created (by hand) a bit-sliced 32-bit RISC-V datapath using the FreePDK45 library and Cadence Virtuoso. The datapath uses a Harvard architecture, meaning that the instruction and data use different memory ports. The register file is write on low clock, read on high clock. Starting from the ground up, I first created basic cells like NAND2, NOR2, MUX2, DFF, etc. These were put together to make 1-bit modules like a register, alu, pc, etc. After integrating these into a one row bitslice, I slapped 32 of them together to make the full datapath. (Of course it wasn’t that simple)

Basic cells

Shown below is a subset of all the basic cells I created.

Bitslice Modules

Some noteworthy bitslice modules are shown below.

Full Bitslice

Full Datapath

Stacking 32 bitslices and connecting control and I/O signals gives us this lovely mess. I also had to rework the shifter many times to achieve the nice looking pattern shown below.

Acknowledgements

Thanks to classmates/friends Jake Cheng, Amaan Shah, and Jack Tipping for staying many days and nights in Grainger 4th floor working on this abomination. Also thanks to TA Stanley Wu for creating this mental torture device!